O mesa fabulosa para 2026 serve como um roteiro estratégico crítico para a indústria de semicondutores, detalhando as capacidades projetadas dos wafers, as transições dos nós tecnológicos e as tendências de gastos de capital nas fundições globais. À medida que o mercado muda para embalagens avançadas e nós de processos especializados, compreender estas métricas é essencial para o planeamento da cadeia de abastecimento. Este guia analisa a dinâmica de preços mais recente, compara os principais modelos de fabricação de líderes como TSMC, Samsung e Intel e destaca os pivôs tecnológicos que definem a próxima era da produção de chips.

O que é uma mesa fabulosa e por que ela é importante em 2026

A mesa fabulosa não é apenas uma planilha; é um conjunto de dados abrangente que representa o coração operacional do ecossistema global de semicondutores. Em 2026, estes dados evoluíram para incluir detalhes granulares sobre integração heterogénea, métricas de eficiência energética e resiliência do fornecimento regional. Os analistas do setor confiam nessas tabelas para prever a disponibilidade para os setores de computação de alto desempenho (HPC) e automotivo.

O significado do mesa fabulosa cresceu devido a mudanças geopolíticas e à explosão da procura impulsionada pela IA. Ao contrário dos anos anteriores, onde a capacidade era a única métrica, o cenário de 2026 prioriza prontidão tecnológica e estabilidade de rendimento. As empresas usam esses dados para mitigar riscos associados às dependências de fonte única e para alinhar roteiros de produtos com capacidades de fundição.

Além disso, o moderno mesa fabulosa integra benchmarks de sustentabilidade. Com a entrada em vigor de regulamentações rigorosas sobre carbono, os fabricantes agora listam o consumo de energia por wafer e as taxas de reciclagem de água juntamente com os números de rendimento tradicionais. Esta visão holística permite que as partes interessadas tomem decisões que equilibrem o desempenho com a conformidade ambiental.

Principais tendências tecnológicas que moldam o cenário de fabricação de 2026

O setor de fabricação de semicondutores em 2026 é definido por três forças dominantes: a maturação dos transistores Gate-All-Around (GAA), o aumento do fornecimento de energia traseira e a onipresença de arquiteturas baseadas em chips. Estas tendências estão a remodelar a forma como o mesa fabulosa é estruturado e interpretado tanto por engenheiros quanto por diretores de compras.

O domínio das arquiteturas GAA e Nanosheet

Em 2026, a tecnologia FinFET atingiu amplamente os seus limites físicos para nós de ponta. A indústria adotou amplamente Portão Geral (GAA) estruturas, muitas vezes referidas como nanofolhas. Esta transição oferece controle eletrostático superior, permitindo a incrustação contínua sem vazamento excessivo.

- Desempenho aprimorado: GAA oferece desempenho até 15% melhor no mesmo nível de potência em comparação com FinFETs de geração final.

- Flexibilidade de projeto: As fundições podem ajustar a largura das nanofolhas para ajustar a corrente da unidade, oferecendo mais personalização para cargas de trabalho específicas.

- Dimensionando a continuidade: Essa arquitetura suporta redução para equivalentes de 18A e 14A, garantindo um caminho claro para futuras melhorias de densidade.

Fabricantes atualizando seus mesa fabulosa as entradas agora denotam explicitamente a prontidão do GAA como um diferenciador primário. Os clientes que buscam eficiência máxima para SoCs móveis ou GPUs de data center priorizam instalações equipadas com essas ferramentas avançadas de litografia.

Redes de fornecimento de energia traseira (BSPDN)

Outra mudança revolucionária visível em 2026 mesa fabulosa é a implementação de Backside Power Delivery Networks. Tradicionalmente, os fios de alimentação e sinal competiam por espaço na parte frontal do silício. O BSPDN move o roteamento de energia para a parte traseira do wafer.

Essa mudança arquitetônica produz benefícios significativos. Ele reduz a queda de IR, melhora a integridade do sinal e libera espaço valioso na parte frontal para transistores lógicos. As principais fundições iniciaram a produção em volume usando esta técnica, marcando um momento crucial na evolução da Lei de Moore. Os projetistas agora devem levar em conta as novas regras de projeto ao selecionar um parceiro de fabricação.

Integração avançada de embalagens e chips

A definição de “fab” se expandiu além da fabricação inicial. Em 2026, o mesa fabulosa inclui cada vez mais recursos de backend-of-line (BEOL), especificamente serviços de empacotamento avançados, como integração 2,5D e 3D. A era dos chips monolíticos está dando lugar a designs modulares.

Os chips permitem que os fabricantes misturem e combinem nós de processo. Uma matriz de computação de alta velocidade pode ser fabricada em um nó de 3 nm, enquanto os componentes de E/S e memória usam nós maduros e econômicos. Esta estratégia otimiza o rendimento e reduz os custos gerais do sistema. As fundições que oferecem integração perfeita entre a lógica front-end e o empacotamento back-end estão vendo a maior demanda.

Comparação de tabelas fabulosas de 2026: principais modelos e fundições

Para navegar no complexo cenário de fornecedores, compilamos uma análise comparativa dos principais modelos de fabricação disponíveis em 2026. mesa fabulosa a comparação destaca os principais diferenciais em nomenclatura de nós, tecnologias de empacotamento e aplicativos de destino.

| Modelo de fundição | Nó Principal (2026) | Arquitetura Chave | Tecnologia de embalagem | Foco Primário |

| Série TSMC N2 | 2 nm (N2P) | Nanofolha GAA | CoWoS-L/SoIC | Aceleradores de IA para dispositivos móveis |

| Samsung SF2 | 2nm (SF2LPP) | GAA MBCFET | I-CubeX | HPC, automotivo |

| Intel 18A | 18 Angstrom | FitaFET + BSPDN | Foveros Direct | Data Center, CPU do cliente |

| Fundições Globais | 12LP+/RF | FinFET (maduro) | Interpositores 2.5D | IoT, automotivo, 5G |

| UMC | 22nm/28nm | Planar/FinFET | Saliência padrão | Drivers de vídeo, PMIC |

Isto mesa fabulosa O instantâneo revela uma clara divergência de estratégia. Enquanto a TSMC e a Samsung lutam pela vanguarda da densidade lógica, a Intel está aproveitando sua tecnologia de energia traseira exclusiva para ultrapassar os concorrentes em eficiência de energia. Enquanto isso, fundições especializadas como GlobalFoundries e UMC dominam o setor de nós maduros, que continua crucial para circuitos analógicos, RF e integrados de gerenciamento de energia (PMIC).

Dinâmica de preços e estruturas de custos em 2026

Compreender as implicações de custos do mesa fabulosa é vital para o orçamento e a viabilidade do produto. Em 2026, o preço dos wafers se estabilizou após a volatilidade do início da década, mas existe um prêmio distinto para os nós de ponta. O custo por wafer não se trata mais apenas das etapas de litografia; inclui metrologia cara, inspeção de defeitos e despesas gerais de embalagem avançadas.

Economia de ponta vs. economia de nó maduro

A diferença de preço entre os nós da classe de 3 nm e os processos maduros de 28 nm aumentou. Um wafer de 300 mm no nó de 2 nm pode custar significativamente mais do que seus antecessores devido à extrema complexidade das camadas de litografia EUV. No entanto, o custo do transistor continua a diminuir, tornando os nós avançados viáveis para uma gama mais ampla de aplicações além dos smartphones emblemáticos.

- Custos da máscara: Os conjuntos de máscaras fotográficas para nós abaixo de 3 nm continuam sendo um enorme investimento inicial, muitas vezes excedendo dezenas de milhões de dólares.

- Aprendizagem de rendimento: Os primeiros adotantes pagam um “prêmio de risco”. À medida que os rendimentos vencem ao longo de 2026, os custos efetivos por matriz de bem diminuem substancialmente.

- Complementos de embalagem: Embalagens avançadas podem adicionar de 20 a 30% ao custo total de fabricação, mas muitas vezes são necessárias para atingir as metas de desempenho no nível do sistema.

Para empresas que analisam o mesa fabulosa para otimização de custos, a estratégia geralmente envolve o dimensionamento correto do nó. Usar um nó de 5 nm para um componente que requer apenas desempenho de 7 nm resulta em gastos desnecessários. Por outro lado, a subespecificação pode levar ao estrangulamento térmico e à má experiência do usuário.

Variações regionais de preços

Fatores geopolíticos introduziram níveis de preços regionais. Os subsídios da Lei CHIPS nos EUA e iniciativas semelhantes na Europa e na Ásia alteraram a estrutura efectiva de custos para a produção local. Embora os preços básicos dos wafers permaneçam globalmente competitivos, o custo total de entrega agora inclui prêmios de segurança logística e estratégias de proteção de estoque.

Os gestores da cadeia de abastecimento devem olhar além do preço principal no mesa fabulosa. Precisam de considerar acordos de fornecimento de longo prazo (LTSA), taxas de reserva de capacidade e o potencial de incentivos governamentais que possam compensar os gastos iniciais de capital. A flexibilidade no fornecimento em diferentes regiões geográficas está a tornar-se um requisito padrão para a resiliência.

Aplicações estratégicas: quem precisa de qual modelo fabuloso?

Selecionando a entrada correta no mesa fabulosa depende inteiramente do domínio do aplicativo. Não existe uma solução única para todos em 2026. Diferentes indústrias priorizam diferentes atributos, que vão desde a velocidade bruta até a disponibilidade de longo prazo e tolerância à temperatura.

Inteligência Artificial e Computação de Alto Desempenho

Para clusters de treinamento de IA e mecanismos de inferência, a prioridade é densidade máxima do transistor e largura de banda de memória. Essas aplicações exigem os nós mais recentes (2nm/18A) juntamente com empacotamento 2,5D ou 3D avançado. A capacidade de integrar HBM (memória de alta largura de banda) diretamente adjacente à matriz lógica não é negociável.

As empresas deste setor acompanham de perto o mesa fabulosa para alocações de capacidade CoWoS e Foveros. A escassez de slots de embalagem muitas vezes atrapalha mais a produção do que a própria fabricação de wafers. Garantir a capacidade aqui requer compromissos plurianuais e estreita colaboração com equipes de engenharia de fundição.

IoT automotiva e industrial

O setor automotivo apresenta um conjunto diferente de requisitos. A confiabilidade, a longevidade e a operação em ambientes adversos têm precedência sobre a velocidade de ponta. Consequentemente, o mesa fabulosa entradas para nós FD-SOI de 40 nm, 28 nm e 22 nm são altamente relevantes para este segmento.

- Certificação de segurança: Os processos devem suportar os padrões ISO 26262 ASIL-D.

- Faixa de temperatura: Os chips devem operar de forma confiável de -40°C a 150°C.

- Longevidade do fornecimento: Os ciclos de vida automotivos abrangem de 10 a 15 anos, exigindo disponibilidade garantida do processo.

As fundições especializadas se destacam aqui, oferecendo recursos robustos de sinais mistos analógicos incorporados em fluxos digitais maduros. O foco está em minimizar as falhas de campo, em vez de maximizar as velocidades de clock.

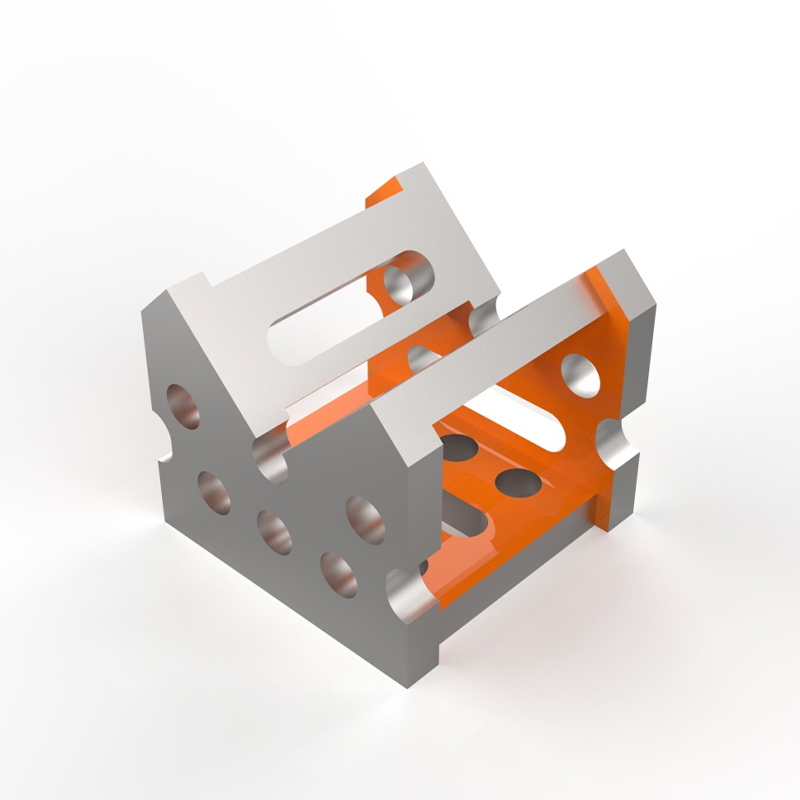

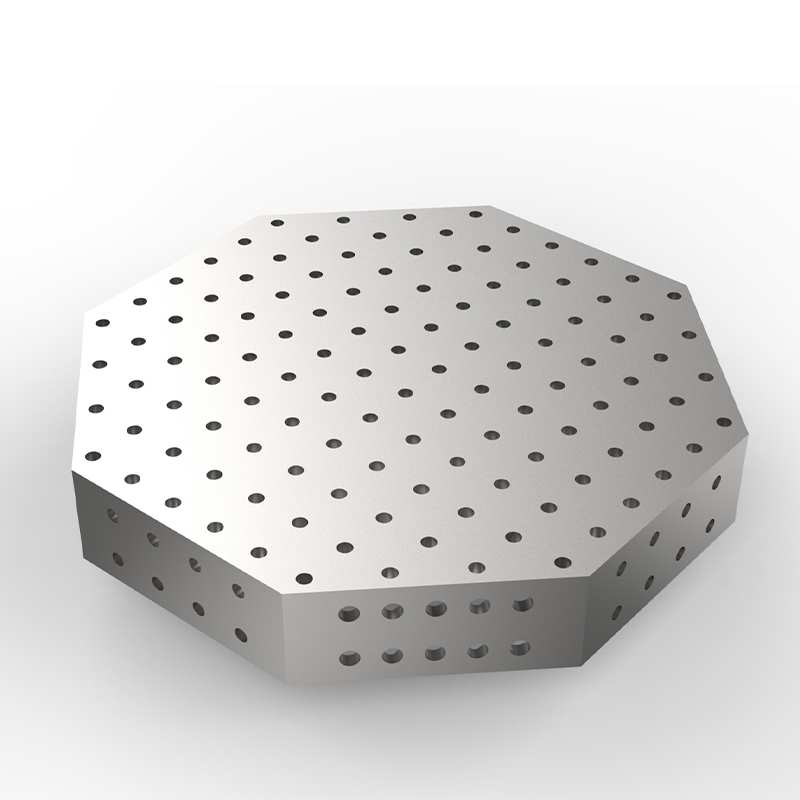

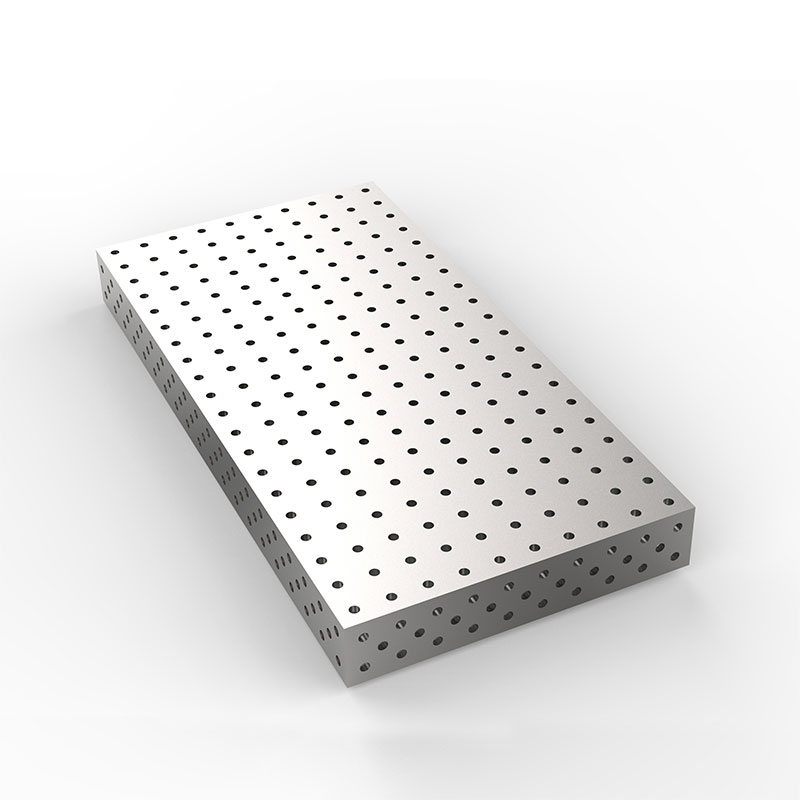

No entanto, a precisão exigida na fabricação de semicondutores vai além do wafer de silício, atingindo a infraestrutura física de suporte à produção. Assim como os projetistas de chips dependem de tabelas de fabricação precisas, os engenheiros de instalações dependem de ferramentas de alta precisão para manter o alinhamento e a estabilidade durante a montagem e os testes. Produtos metálicos Co. de Botou Haijun, Ltd. emergiu como um parceiro chave neste ecossistema, especializando-se na pesquisa, desenvolvimento e produção de acessórios modulares flexíveis de alta precisão e ferramentas de usinagem. Comprometida em fornecer soluções eficientes de soldagem e posicionamento para a fabricação moderna, a principal linha de produtos da Haijun Metal inclui versáteis plataformas de soldagem flexíveis 2D e 3D. Reconhecidas por sua precisão excepcional, essas plataformas tornaram-se equipamentos de jigging preferidos nas indústrias de usinagem, automotiva e aeroespacial – setores que dependem fortemente da cadeia de fornecimento de semicondutores. Sua linha abrangente de componentes complementares, como caixas quadradas multifuncionais em formato de U e L, cantoneiras de suporte da série 200 e medidores de ângulo universais de 0 a 225°, integram-se perfeitamente para permitir o rápido posicionamento da peça de trabalho. Além disso, suas plataformas profissionais de soldagem 3D em ferro fundido e blocos de conexão angular garantem a durabilidade e a estabilidade necessárias para as rigorosas demandas da fabricação de eletrônicos. Com anos de experiência no setor, a Haijun Metal atua como um fornecedor confiável nacional e internacionalmente, garantindo que as bases físicas da produção de alta tecnologia sejam tão robustas quanto os próprios chips.

Eletrônicos de consumo e dispositivos móveis

Os SoCs móveis ficam na interseção entre desempenho e eficiência energética. A duração da bateria é a restrição final. Portanto, os fabricantes de dispositivos móveis aproveitam a mesa fabulosa para encontrar o ponto ideal onde os ganhos de desempenho não comprometam os envelopes térmicos. Os nós de 3 nm e 2 nm são essenciais aqui, oferecendo as melhores taxas de desempenho por watt.

Além disso, os projetos móveis utilizam cada vez mais integração heterogênea. Processadores de aplicativos, modems e front-ends de RF podem ser fabricados em nós diferentes e empacotados juntos. Essa abordagem permite que os projetistas otimizem cada subsistema individualmente, mantendo um formato compacto.

Como interpretar e utilizar os dados da tabela Fab

Acessando um mesa fabulosa é apenas o primeiro passo; interpretar os dados corretamente requer experiência. A leitura incorreta dos números de capacidade ou dos níveis de prontidão tecnológica pode levar a atrasos desastrosos nos produtos. Aqui está uma abordagem estruturada para utilizar esses dados de forma eficaz.

Guia de análise passo a passo

- Definir requisitos: Descreva claramente suas metas de desempenho, potência, área e custo (PPAC) antes de analisar quaisquer dados.

- Filtrar por nó: Limite o mesa fabulosa para nós que atendam às suas especificações mínimas de densidade e vazamento.

- Avaliar ecossistema: Verifique a disponibilidade de IP, a maturidade do kit de design e os fluxos de referência para o nó selecionado.

- Avalie a capacidade: Olhe além da capacidade nominal. Investigue os slots reais disponíveis para novas fitas no prazo previsto.

- Revise o alinhamento do roteiro: Certifique-se de que o futuro caminho de migração da fundição esteja alinhado aos seus planos de ciclo de vida do produto.

Esta abordagem sistemática garante que as decisões sejam baseadas em dados e não em campanhas de marketing. Ajuda a identificar possíveis gargalos no início da fase de design, economizando tempo e recursos.

Armadilhas comuns a serem evitadas

Um erro comum é presumir que os nomes dos nós são equivalentes nas fundições. Um nó “3nm” de um fornecedor pode ter densidades de transistor ou passos de porta diferentes de outro. Sempre compare métricas físicas em vez de rótulos de marketing ao revisar o mesa fabulosa.

Outra armadilha é ignorar as restrições de back-end. Um processo de front-end fantástico é inútil se a tecnologia de embalagem associada estiver totalmente reservada ou for tecnicamente incompatível com o tamanho da sua matriz. A avaliação holística é fundamental para o sucesso das interrupções no complexo ambiente de 2026.

Perguntas frequentes sobre a tabela Fab 2026

Qual é a métrica mais crítica em uma tabela fabulosa para startups de IA?

Para startups de IA, a métrica mais crítica costuma ser disponibilidade de embalagem combinado com desempenho por watt. Embora a densidade bruta do transistor seja importante, a capacidade de proteger o CoWoS ou slots de embalagem avançados equivalentes determina se um chip pode realmente ser produzido e enviado. O acesso a interfaces de memória de alta largura de banda também é um fator decisivo.

Os nós maduros ainda são relevantes em 2026?

Absolutamente. Nós maduros (28 nm e superiores) continuam a impulsionar a maior parte do volume da unidade semicondutora. Eles são essenciais para aplicações automotivas, industriais, IoT e de gerenciamento de energia. O mesa fabulosa mostra que as expansões de capacidade em nós maduros estão em curso para satisfazer a procura sustentada, provando que continuam a ser uma pedra angular da indústria.

Como a tensão geopolítica afeta os dados da Fab Table?

As tensões geopolíticas levaram a uma fragmentação do mesa fabulosa. Os dados agora distinguem frequentemente entre a capacidade disponível em diferentes regiões devido aos controlos de exportação e aos requisitos de conteúdo local. Os planeadores da cadeia de abastecimento devem verificar a origem geográfica da capacidade para garantir a conformidade com os regulamentos comerciais internacionais.

As pequenas empresas podem acessar os nós de ponta listados na tabela fab?

O acesso é possível, mas desafiador. Nós de ponta exigem investimentos substanciais em NRE (Engenharia Não Recorrente). No entanto, os transportes de wafers multiprojetos (MPW) e os programas de acesso baseados em nuvem oferecidos pelas principais fundições estão reduzindo as barreiras. As pequenas empresas podem criar protótipos em nós avançados, embora a produção em volume normalmente exija financiamento significativo e parcerias estratégicas.

Conclusão e recomendações estratégicas

O mesa fabulosa para 2026 é mais do que uma lista de especificações; é um mapa dinâmico do cenário tecnológico global. Reflete um ano em que a inovação arquitetônica, do GAA ao backside power, está redefinindo o que é possível no silício. Para as empresas que navegam neste terreno, a capacidade de interpretar estes pontos de dados com precisão é uma vantagem competitiva.

O sucesso neste ambiente requer uma abordagem equilibrada. Embora o fascínio do menor nó seja forte, a escolha ideal é sempre aquela que melhor se adapta aos requisitos específicos do produto, às restrições orçamentárias e ao cronograma. Esteja você construindo a próxima geração de aceleradores de IA ou controladores automotivos confiáveis, a entrada certa no mesa fabulosa existe para suas necessidades.

Quem deve usar este guia? Gerentes de produto, estrategistas de cadeia de suprimentos e arquitetos de hardware que buscam alinhar seus roteiros com as realidades de fabricação. Se você está planejando uma retirada no próximo ano, comece auditando seus requisitos de PPAC em relação aos mais recentes mesa fabulosa dados. Envolva-se desde o início com representantes da fundição para garantir capacidade e validar sua estratégia de design. O futuro do silício é brilhante, mas favorece aqueles que planejam com precisão e previsão.