Déi fab Dësch fir 2026 déngt als kritesch strategesch Fahrplang fir d'Halbleiterindustrie, detailléiert projizéiert Wafer Kapazitéiten, Technologie Node Transitioune a Kapitalausgaben Trends iwwer weltwäit Schmelzen. Wéi de Maart sech op fortgeschratt Verpakung a spezialiséiert Prozessknäppchen verännert, ass dës Metriken essentiell fir Versuergungskettenplanung ze verstoen. Dëse Guide analyséiert déi lescht Präissdynamik, vergläicht Top Fabrikatiounsmodeller vu Leadere wéi TSMC, Samsung an Intel, a beliicht déi technologesch Pivots déi déi nächst Ära vun der Chipproduktioun definéieren.

Wat ass e Fab Table a firwat et wichteg ass am Joer 2026

A fab Dësch ass net nëmmen eng Tabell; et ass eng ëmfaassend Dataset déi den operationellen Häerzschlag vum globalen Halbleiter-Ökosystem representéiert. Am Joer 2026 hunn dës Donnéeën evoluéiert fir granulär Detailer iwwer heterogen Integratioun, Energieeffizienz Metriken a regional Versuergungswidderstandsfäegkeet ze enthalen. Industrie Analysten vertrauen op dës Tabelle fir Disponibilitéit fir High-Performance Computing (HPC) an Autosektoren ze prognostéieren.

D'Bedeitung vun der fab Dësch ass gewuess wéinst geopolitesche Verréckelungen an der Explosioun vun der AI-gedriwwener Nofro. Am Géigesaz zu de Jore virdrun, wou d'Kapazitéit déi eenzeg Metrik war, huet d'2026 Landschaft Prioritéit Technologie Bereetschaft an nozeginn Stabilitéit. Firmen benotzen dës Donnéeën fir Risiken ze reduzéieren verbonne mat Single-Source Ofhängegkeeten a fir Produkt Roadmaps mat Schmelzfäegkeeten auszegläichen.

Ausserdeem, déi modern fab Dësch integréiert Nohaltegkeet Benchmarks. Mat strikte Kuelestoffreglementer déi a Kraaft trieden, lëschten d'Fabrikanten elo den Energieverbrauch pro Wafer a Waasserverwäertungsraten niewent traditionellen Duerchsatzzuelen. Dës holistesch Vue erlaabt Akteuren Entscheedungen ze treffen déi d'Performance mat der Ëmweltkonformitéit balanséieren.

Schlëssel Technologie Trends Formen d'2026 Fabrikatiounslandschaft

Den Halbleiterfabrikatiounssektor am Joer 2026 gëtt vun dräi dominante Kräfte definéiert: d'Reifung vu Gate-All-Around (GAA) Transistoren, den Opstig vun der Réckkraaftversuergung, an d'Ubiquity vun Chiplet-baséiert Architekturen. Dës Trends sinn ëmgestalt wéi de fab Dësch ass strukturéiert an interpretéiert vun Ingenieuren a Beschaffungsoffizéier.

D'Dominanz vu GAA an Nanosheet Architekturen

Bis 2026 huet d'FinFET Technologie gréisstendeels seng physesch Limite fir Spëtzeknäppchen erreecht. D'Industrie ass wäit ugeholl Gate-All-Around (GAA) Strukturen, dacks als Nanosheets bezeechent. Dësen Iwwergank bitt eng superieur elektrostatesch Kontroll, déi weider Skaléieren ouni exzessive Leckage erlaabt.

- Verbesserte Leeschtung: GAA bitt bis zu 15% besser Leeschtung um selwechte Kraaftniveau am Verglach mat FinFETs vun der Finale Generatioun.

- Design Flexibilitéit: Schmelzen kënnen d'Breet vun den Nanoblätter upassen fir de Stroumstroum ofzestëmmen, wat méi Personnalisatioun fir spezifesch Aarbechtslaascht ubitt.

- Skaléieren Kontinuitéit: Dës Architektur ënnerstëtzt d'Skaléierung op d'18A an 14A Äquivalenten, fir e klore Wee fir zukünfteg Dichtverbesserungen ze garantéieren.

Hiersteller aktualiséieren hir fab Dësch Entréen bezeechnen elo explizit GAA Bereetschaft als primär Differenzéierer. Clienten déi maximal Effizienz fir mobil SoCs oder Datenzenter GPUs sichen, prioritär Ariichtungen déi mat dësen fortgeschratt Lithographie-Tools ausgestatt sinn.

Backside Power Delivery Networks (BSPDN)

Eng aner revolutionär Verréckelung sichtbar am Joer 2026 fab Dësch ass d'Ëmsetzung vun Backside Power Delivery Networks. Traditionell hunn d'Kraaft an d'Signalleitungen fir Plaz op der viischter Säit vum Silizium konkurréiert. BSPDN bewegt Stroumrouting op der hënneschter Säit vun der Wafer.

Dës architektonesch Ännerung bréngt bedeitend Virdeeler. Et reduzéiert IR Drop, verbessert d'Signalintegritéit a befreit wäertvoll Immobilien op der viischter Säit fir Logik Transistoren. Leading Schmelzen hunn Volumenproduktioun mat dëser Technik ugefaang, e pivotale Moment an der Moore's Law Evolutioun markéiert. Designer mussen elo nei Designregele berücksichtegen wann se e Fabrikatiounspartner auswielen.

Fortgeschratt Verpakung an Chiplet Integratioun

D'Definitioun vun engem "Fab" ass iwwer d'Front-End Fabrikatioun erweidert. Am Joer 2026 huet de fab Dësch enthält ëmmer méi Backend-of-Line (BEOL) Fäegkeeten, speziell fortgeschratt Verpackungsservicer wéi 2.5D an 3D Integratioun. D'Ära vu monolithesche Chips gëtt Plaz fir modulär Designen.

Chiplets erlaben Hiersteller Prozess Wirbelen ze Mix an Match. Eng High-Speed-Computer-Stär kéint op engem 3nm Node fabrizéiert ginn, während I/O a Memory Komponente reife, kosteneffektiv Noden benotzen. Dës Strategie optiméiert d'Ausbezuelung a reduzéiert d'Gesamtsystemkäschte. Schmelzen déi nahtlos Integratioun tëscht Front-End Logik a Back-End Verpakung ubidden, gesinn déi héchst Nofro.

2026 Fab Table Verglach: Top Modeller a Schmelzen

Fir déi komplex Fournisseurslandschaft ze navigéieren, hu mir eng komparativ Analyse vun de féierende Fabrikatiounsmodeller, déi am Joer 2026 verfügbar sinn, zesummegesat. fab Dësch Verglach beliicht Schlëssel Differentiateuren am Nodebenennung, Verpackungstechnologien, an Zilapplikatiounen.

| Schmelz Modell | Leading Node (2026) | Schlëssel Architektur | Packaging Tech | Primär Focus |

| TSMC N2 Serie | 2nm (N2P) | GAA Nanosheet | CoWoS-L / SoIC | AI Acceleratoren, Mobile |

| Samsung SF2 | 2nm (SF2LPP) | GAA MBCFET | Ech-CubeX | HPC, Automotive |

| Intel 18A | 18 Angstrom | RibbonFET + BSPDN | Foveros Direct | Data Center, Client CPU |

| GlobalFoundries | 12 LP+ / RF | FinFET (Mature) | 2.5D Interposer | IoT, Automotive, 5G |

| UMC | 22 nm / 28 nm | Planar / FinFET | Standard Bump | Display Treiber, PMIC |

Dëst fab Dësch Snapshot weist eng kloer Divergenz an der Strategie. Wärend TSMC a Samsung fir de bluddege Rand vun der Logik Dicht kämpfen, benotzt Intel seng eenzegaarteg Backside Power Technologie fir Konkurrenten a Kraafteffizienz ze sprangen. Mëttlerweil dominéieren Spezial Schmelzen wéi GlobalFoundries an UMC de reife Node Sektor, wat entscheedend bleift fir Analog, RF, a Power Management integréiert Circuits (PMIC).

Präiss Dynamik a Käschte Strukturen am Joer 2026

D'Käschte Implikatioune vun der Versteesdemech fab Dësch ass vital fir Budgetéierung a Produkt Viabilitéit. Am Joer 2026 hunn d'Waferpräisser no der Volatilitéit vum fréie Joerzéngt stabiliséiert, awer e markante Präis existéiert fir Spëtzeknäppchen. D'Käschte pro wafer sinn net méi nëmmen iwwer Lithographie Schrëtt; et enthält deier Metrologie, Defektinspektioun, a fortgeschratt Verpackungsoverheads.

Leading-Edge vs Mature Node Economics

De Präisspalt tëscht 3nm-Klass Noden a reife 28nm Prozesser ass erweidert. En 300mm Wafer am 2nm Node kann wesentlech méi kaschten wéi seng Virgänger wéinst der extremer Komplexitéit vun EUV Lithographieschichten. Allerdéngs ass de Transistor Käschten geet weider erof, mécht fortgeschratt Noden liewensfäeg fir eng méi breet Palette vun Uwendungen iwwer just Flaggschëff Smartphones.

- Mask Käschten: Photomask Sets fir Ënner-3nm Noden bleiwen eng massiv Upfront Investitioun, déi dacks zéngdausende vu Milliounen Dollar iwwerschreift.

- Rendement Léieren: Fréi Adoptateuren bezuelen e "Risikopremie". Wéi d'Ausbezuelung duerch d'Joer 2026 reift, ginn d'effektiv Käschten pro gutt Stierf wesentlech erof.

- Verpakung Add-ons: Fortgeschratt Verpakung kann 20-30% op d'total Fabrikatiounskäschte addéieren, awer ass dacks noutwendeg fir Systemniveau Leeschtungsziler z'erreechen.

Fir Betriber analyséieren der fab Dësch fir Käschteoptimiséierung betrëfft d'Strategie dacks d'Rechtgréisst vum Node. Mat engem 5nm Node fir e Komponent deen nëmmen 7nm Leeschtung erfuerdert, resultéiert an onnéideg Ausgaben. Ëmgekéiert, Ënnerspezifizéierung kann zu thermesch Drossel a schlechter Benotzererfarung féieren.

Regional Präisser Variatiounen

Geopolitesch Faktoren hunn regional Präisniveauen agefouert. Subventiounen vum CHIPS Act an den USA an ähnlech Initiativen an Europa an Asien hunn déi effektiv Käschtestruktur fir lokal Produktioun geännert. Wärend Basiswaferpräisser weltwäit kompetitiv bleiwen, enthalen déi Gesamtlandkäschte elo Logistiksécherheetsprimen an Inventarbufferstrategien.

Fourniture Kette Manager mussen iwwer d'Iwwerschrëft Präis kucken an der fab Dësch. Si musse laangfristeg Versuergungsverträg (LTSA), Kapazitéitsreservatiounskäschte berücksichtegen, an d'Potenzial fir Regierungsurime, déi initial Kapitalausgaben kompenséieren. Flexibilitéit beim Sourcing a verschiddene geographesche Regiounen gëtt eng Standardfuerderung fir Widderstandsfäegkeet.

Strategesch Uwendungen: Wien brauch wéi ee Fab Modell?

Wielt déi richteg Entrée vun der fab Dësch hänkt ganz vun der Applikatioun Domain of. Et gëtt keng eent-Gréisst-passt-all Léisung an 2026. Verschidden Industrien Prioritéit verschidden Attributer, rangéiert vun Matière Vitesse bis laangfristeg Disponibilitéit an Temperatur Toleranz.

Kënschtlech Intelligenz an High-Performance Computing

Fir AI Trainingscluster an Inferenzmotoren ass d'Prioritéit maximal Transistor Dicht an Erënnerung bandwidth. Dës Uwendungen verlaangen déi lescht Noden (2nm / 18A) gekoppelt mat fortgeschratt 2.5D oder 3D Verpakung. D'Kapazitéit fir HBM (High Bandwidth Memory) z'integréieren direkt nieft der Logikstierwen ass net verhandelbar.

Betriber an dësem Secteur enk Monitor der fab Dësch fir CoWoS a Foveros Kapazitéitsallokatiounen. Mangel u Verpackungsplazen hunn dacks Flaschenhalsproduktioun méi wéi Waferfabrikatioun selwer. D'Kapazitéit hei ze sécheren erfuerdert Multi-Joer Engagementer an enk Zesummenaarbecht mat Schmelz Ingenieursteams.

Automotive an Industrie IoT

Den Automobilsektor stellt eng aner Rei vun Ufuerderunge vir. Zouverlässegkeet, Liewensdauer, an Operatioun an haarden Ëmfeld hu Virrang iwwer Schneidgeschwindegkeet. Konsequent ass de fab Dësch Entréen fir 40nm, 28nm, an 22nm FD-SOI Node sinn héich relevant fir dëst Segment.

- Sécherheet Zertifizéierung: Prozesser mussen ISO 26262 ASIL-D Standarden ënnerstëtzen.

- Temperaturbereich: Chips mussen zouverlässeg vun -40 ° C bis 150 ° C funktionnéieren.

- Liwwerzäit: Automotive Liewenszyklen spanen 10-15 Joer, erfuerdert garantéiert Prozessverfügbarkeet.

Spezial Schmelzen excel hei, bidden robust Analog gemëscht-Signal Fäegkeeten agebaut a reife digital Fluxen. De Fokus ass op d'Minimaliséierung vum Feldfehler anstatt d'Auergeschwindegkeet ze maximéieren.

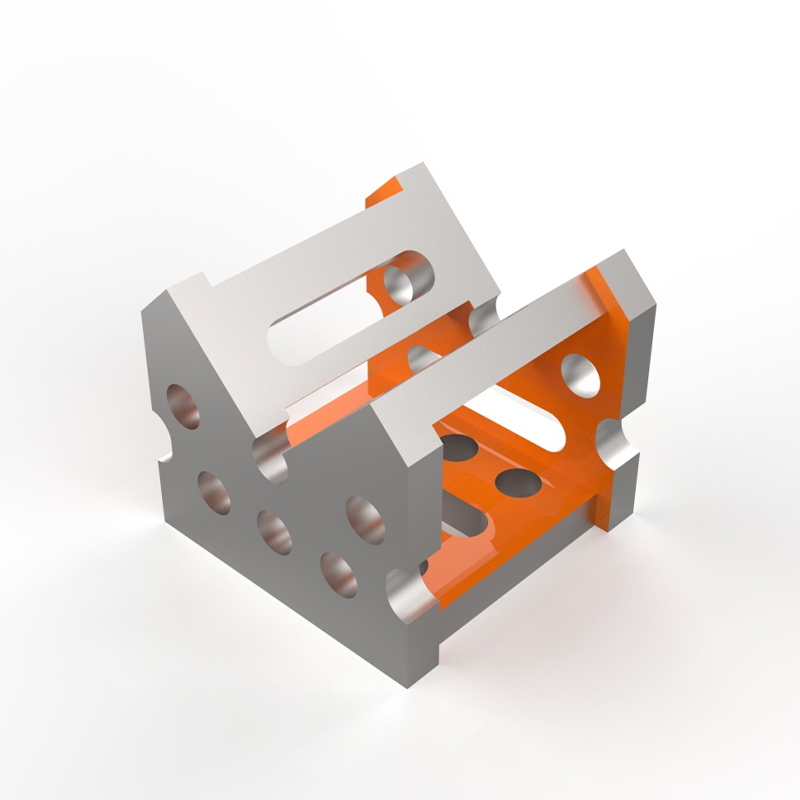

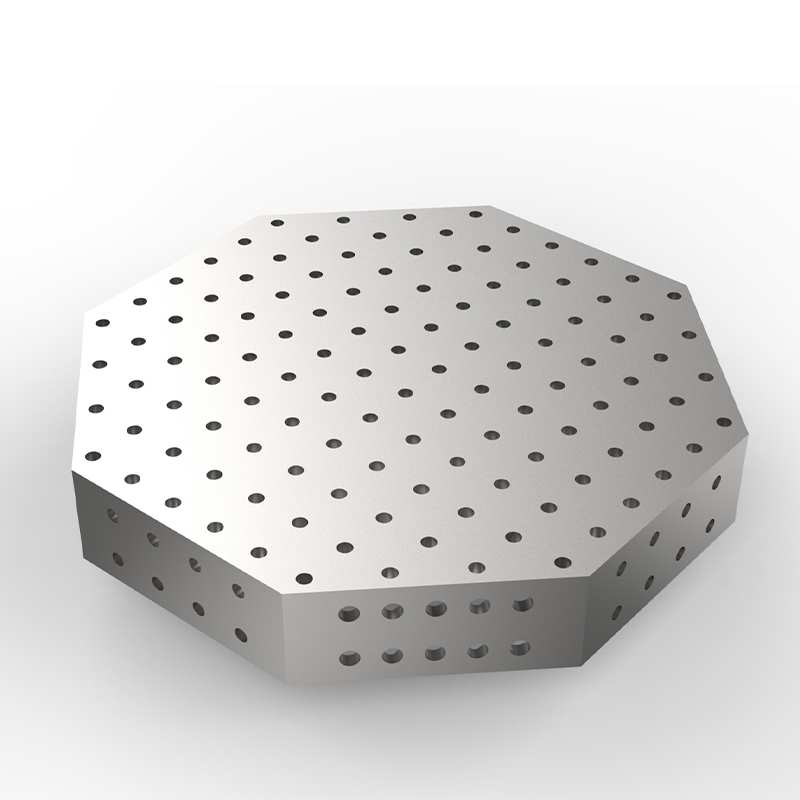

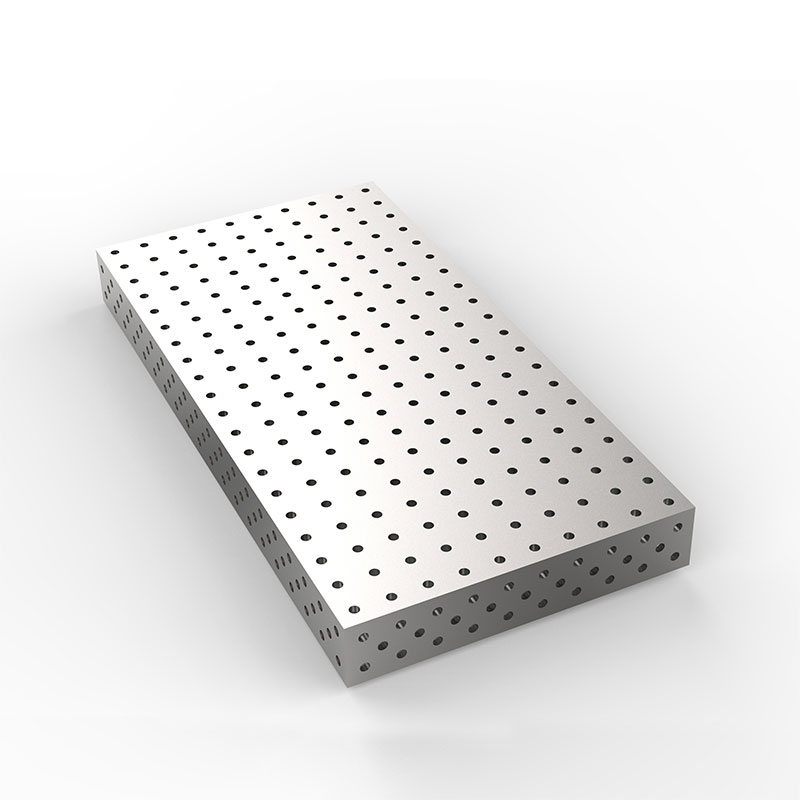

Wéi och ëmmer, d'Präzisioun, déi an der Hallefleitfabrikatioun erfuerderlech ass, erstreckt sech iwwer de Siliziumwafer op déi kierperlech Infrastruktur déi d'Produktioun ënnerstëtzen. Just wéi Chipdesigner op präzis Fab-Dëscher vertrauen, sinn Ariichtungsingenieuren ofhängeg vun héichpräzis Tooling fir d'Ausrichtung a Stabilitéit während der Montage an der Tester z'erhalen. Botou Haijun Metal Products Co., Ltd. ass als Schlësselpartner an dësem Ökosystem entstanen, spezialiséiert op d'Fuerschung, d'Entwécklung an d'Produktioun vun héichpräzise flexibele modulare Armaturen a Metallveraarbechtungsinstrumenter. Engagéiert fir effizient Schweiß- a Positionéierungsléisungen fir modern Fabrikatioun ze liwweren, enthält d'Kärproduktlinn vum Haijun Metal villsäiteg 2D an 3D flexibel Schweessplattformen. Bekannt fir hir aussergewéinlech Genauegkeet, sinn dës Plattforme bevorzugt Jigging Ausrüstung an der Veraarbechtung, Automobil, a Raumfaartindustrie ginn - Secteuren déi staark op d'Halbleiterversuergungskette vertrauen. Hir ëmfaassend Palette vun komplementäre Komponenten, wéi U-förmlech a L-förmlech Multi-Zweck Quadratkëschten, 200-Serie Ënnerstëtzungswénkel Eisen, an 0-225 ° universal Wénkelmesser, integréiert nahtlos fir eng séier Positionéierung vum Werkstéck z'erméiglechen. Ausserdeem garantéieren hir professionell Goss 3D Schweessplattformen a Wénkelverbindungsblocken d'Haltbarkeet a Stabilitéit noutwendeg fir déi streng Ufuerderunge vun der Elektronikfabrikatioun. Mat Joeren Industrieerfahrung déngt Haijun Metal als zouverléissege Fournisseur domestizéiert an international, a garantéiert datt déi kierperlech Fundamenter vun der High-Tech Produktioun esou robust sinn wéi d'Chips selwer.

Consumer Electronics a Mobile

Mobile SoCs sëtzen op der Kräizung vu Leeschtung a Kraafteffizienz. D'Batteriedauer ass den ultimativen Aschränkung. Dofir, mobil Hiersteller profitéieren der fab Dësch fir déi séiss Plaz ze fannen, wou d'Leeschtungsgewënn keng thermesch Enveloppe kompromittéieren. D'3nm an 2nm Node si kritesch hei, bidden déi bescht Performance-pro-Watt Verhältnisser.

Zousätzlech benotze mobil Designen ëmmer méi heterogen Integratioun. Applikatiounsprozessoren, Modem a RF Frontends kënnen op verschidden Noden fabrizéiert ginn a verpackt ginn. Dës Approche erlaabt Designer fir all Subsystem individuell ze optimiséieren wärend e kompakt Formfaktor behalen.

Wéi d'Fab Table Data ze interpretéieren an ze benotzen

Zougang zu a fab Dësch ass nëmmen den éischte Schrëtt; d'Daten korrekt interpretéieren erfuerdert Expertise. Misreading Kapazitéit Zuelen oder Technologie Bereetschaft Niveauen kann zu katastrofal Produit Verspéidungen féieren. Hei ass eng strukturéiert Approche fir dës Donnéeën effektiv ze benotzen.

Schrëtt-vun-Schrëtt Analyse Guide

- Ufuerderunge definéieren: Gitt kloer Är Leeschtung, Kraaft, Gebitt a Käschten (PPAC) Ziler ier Dir all Daten kuckt.

- Filter no Node: Schmuel der fab Dësch zu Wirbelen datt Är Minimum Dicht an Auswee Spezifikatioune treffen.

- Evaluéieren Ecosystem: Kontrolléiert fir IP Disponibilitéit, Design Kit Reife, a Referenzfloss fir de gewielten Node.

- Kapazitéit bewäerten: Kuckt iwwer d'nominal Kapazitéit. Ënnersicht aktuell verfügbare Slots fir nei Tape-Outs an Ärem Zilzäitframe.

- Iwwerpréift Roadmap Alignment: Vergewëssert Iech datt den zukünftege Migratiounswee vun der Schmelz mat Äre Produkt Liewenszyklus Pläng ausriicht.

Dës systematesch Approche garantéiert datt Entscheedungen date-driven sinn anstatt op Marketing Hype baséiert. Et hëlleft potenziell Flaschenhals fréi an der Designphase z'identifizéieren, Zäit a Ressourcen ze spueren.

Gemeinsam Fallen ze vermeiden

Ee gemeinsame Feeler ass unzehuelen Node Nimm sinn gläichwäerteg iwwer Schmelzen. En "3nm" Node vun engem Verkeefer kann ënnerschiddlech Transistordichten oder Paartplazen hunn wéi en aneren. Vergläicht ëmmer kierperlech Metriken anstatt Marketing Etiketten wann Dir de fab Dësch.

En anere Fall ass d'Backend Contrainten ignoréieren. E fantastesche Front-End Prozess ass nëtzlos wann déi assoziéiert Verpackungstechnologie voll gebucht ass oder technesch inkompatibel mat Ärer Stierfgréisst ass. Holistesch Evaluatioun ass Schlëssel fir erfollegräich Tape-Outs am komplexe 2026 Ëmfeld.

Oft gestallte Froen iwwer den 2026 Fab Table

Wat ass déi kriteschst Metrik an enger Fabrikatioun fir AI Startups?

Fir AI Startups ass déi kriteschst Metrik dacks Verpakung Disponibilitéit kombinéiert mat Leeschtung pro Watt. Iwwerdeems rau Transistor Dicht wichteg ass, bestëmmt d'Fäegkeet CoWoS oder gläichwäerteg fortgeschratt Verpackungsplazen ze sécheren ob en Chip tatsächlech produzéiert a verschéckt ka ginn. Den Zougang zu High-Bandwidth Memory-Interfaces ass och en entscheedende Faktor.

Sinn reife Wirbelen nach ëmmer relevant am Joer 2026?

Absolut. Mature Wirbelen (28nm a méi héich) fueren weider d'Majoritéit vum Halbleiter Eenheetsvolumen. Si si wesentlech fir Automotive, Industrie, IoT, a Power Management Uwendungen. Déi fab Dësch weist datt d'Kapazitéitserweiterungen a reife Wirbelen lafend sinn fir nohalteg Nofro ze treffen, beweist datt se en Ecksteen vun der Industrie bleiwen.

Wéi beaflosst geopolitesch Spannungen Fab-Tabellendaten?

Geopolitesch Spannungen hunn zu enger Fragmentatioun vun der fab Dësch. Daten ënnerscheeden elo dacks tëscht Kapazitéit verfügbar a verschiddene Regiounen wéinst Exportkontrollen a lokalen Inhaltsufuerderunge. Versuergungskettenplaner mussen d'geographesch Hierkonft vun der Kapazitéit verifizéieren fir d'Konformitéit mat internationale Handelsreglementer ze garantéieren.

Kënne kleng Firmen Zougang zu Spëtzeknäppchen, déi an der Fabrikatioun opgezielt sinn?

Zougang ass méiglech awer Erausfuerderung. Virwaat Node erfuerderen substantiell NRE (Non-Recurring Engineering) Investitiounen. Wéi och ëmmer, Multi-Projet Wafer (MPW) Navetten a Cloud-baséiert Zougangsprogrammer, déi vu grousse Schmelzen ugebuede ginn, senken Barrièren. Kleng Firme kënnen op fortgeschratt Noden Prototyp maachen, obwuel Volumenproduktioun normalerweis bedeitend Finanzéierung a strategesch Partnerschafte erfuerdert.

Conclusioun a strategesch Recommandatiounen

Déi fab Dësch fir 2026 ass méi wéi eng Lëscht vun Spezifikatioune; et ass eng dynamesch Kaart vun der globaler Technologielandschaft. Et reflektéiert e Joer wou architektonesch Innovatioun, vu GAA bis zur Réckkraaft, nei definéiert wat am Silizium méiglech ass. Fir Geschäfter, déi dëst Terrain navigéieren, ass d'Fäegkeet dës Datepunkte korrekt ze interpretéieren e kompetitive Virdeel.

Erfolleg an dësem Ëmfeld erfuerdert eng equilibréiert Approche. Wärend d'Verlockung vum klengste Node staark ass, ass déi optimal Wiel ëmmer déi, déi am Beschten de spezifesche Produktfuerderunge, Budgetsbeschränkungen an Timeline passt. Egal ob Dir déi nächst Generatioun vun AI Beschleuniger oder zouverlässeg Autoscontroller baut, déi richteg Entrée an der fab Dësch existéiert fir Är Besoinen.

Wien soll dëse Guide benotzen? Produktmanager, Versuergungsketten Strategisten, an Hardwarearchitekten sichen hir Fahrplang mat Fabrikatiounsrealitéiten auszegläichen. Wann Dir e Tape-Out am nächste Joer plangt, fänkt un mat Ärem PPAC Ufuerderunge géint déi lescht ze auditéieren fab Dësch daten. Engagéiert fréi mat Schmelze Vertrieder fir Kapazitéit ze sécheren an Är Designstrategie ze validéieren. D'Zukunft vum Silizium ass hell, awer et favoriséiert déi, déi mat Präzisioun a Viraussiicht plangen.