The parádní stůl pro rok 2026 slouží jako kritický strategický plán pro polovodičový průmysl, který podrobně popisuje projektované kapacity waferů, přechody technologických uzlů a trendy kapitálových výdajů napříč globálními slévárnami. Jak se trh posouvá směrem k pokročilému balení a specializovaným procesním uzlům, pochopení těchto metrik je zásadní pro plánování dodavatelského řetězce. Tato příručka analyzuje nejnovější dynamiku cen, porovnává špičkové výrobní modely od lídrů, jako jsou TSMC, Samsung a Intel, a zdůrazňuje technologické klíčové prvky definující další éru výroby čipů.

Co je skvělý stůl a proč na něm záleží v roce 2026

A parádní stůl není pouze tabulkový procesor; je to komplexní datový soubor představující provozní tep globálního polovodičového ekosystému. V roce 2026 se tato data vyvinula tak, aby zahrnovala podrobné podrobnosti o heterogenní integraci, metrikách energetické účinnosti a regionální odolnosti dodávek. Oboroví analytici se na tyto tabulky spoléhají při předpovědi dostupnosti pro vysoce výkonné výpočetní systémy (HPC) a automobilový průmysl.

Význam toho parádní stůl vzrostla kvůli geopolitickým posunům a explozi poptávky řízené AI. Na rozdíl od předchozích let, kdy byla kapacita jediným měřítkem, upřednostňuje prostředí pro rok 2026 technologická připravenost a stabilita výnosu. Společnosti používají tato data ke zmírnění rizik spojených se závislostmi na jediném zdroji a ke sladění produktových plánů s možnostmi slévárny.

Navíc moderní parádní stůl integruje měřítka udržitelnosti. Vzhledem k tomu, že vstoupily v platnost přísné uhlíkové předpisy, výrobci nyní uvádějí spotřebu energie na wafer a míru recyklace vody vedle tradičních čísel propustnosti. Tento holistický pohled umožňuje zúčastněným stranám činit rozhodnutí, která vyvažují výkon s dodržováním požadavků na životní prostředí.

Klíčové technologické trendy utvářející krajinu výroby v roce 2026

Sektor výroby polovodičů v roce 2026 je definován třemi dominantními silami: dozráváním tranzistorů Gate-All-Around (GAA), vzestupem dodávky energie na zadní straně a všudypřítomností architektur založených na čipech. Tyto trendy přetvářejí způsob parádní stůl je strukturován a interpretován jak inženýry, tak úředníky pro zadávání zakázek.

Dominance GAA a nanovrstvových architektur

Do roku 2026 technologie FinFET z velké části dosáhla svých fyzických limitů pro špičkové uzly. Průmysl široce přijal Gate-All-Around (GAA) struktur, často označovaných jako nanovrstvy. Tento přechod nabízí vynikající elektrostatickou kontrolu, což umožňuje nepřetržité škálování bez nadměrného úniku.

- Vylepšený výkon: GAA poskytuje až o 15 % lepší výkon při stejné úrovni výkonu ve srovnání s FinFETy finální generace.

- Flexibilita designu: Slévárny mohou upravit šířku nanovrstvy, aby vyladily proud pohonu, což nabízí více přizpůsobení pro konkrétní pracovní zatížení.

- Kontinuita škálování: Tato architektura podporuje zmenšení na ekvivalenty 18A a 14A, což zajišťuje jasnou cestu pro budoucí zlepšení hustoty.

Výrobci aktualizují své parádní stůl položky nyní explicitně označují připravenost GAA jako primární diferenciátor. Klienti, kteří hledají maximální efektivitu mobilních SoC nebo GPU datových center, upřednostňují zařízení vybavená těmito pokročilými litografickými nástroji.

Backside Power Delivery Networks (BSPDN)

Další revoluční posun viditelný v roce 2026 parádní stůl je implementace Backside Power Delivery Networks. Tradičně o místo na přední straně křemíku soupeřily napájecí a signální vodiče. BSPDN přesouvá směrování energie do zadní části waferu.

Tato architektonická změna přináší významné výhody. Snižuje pokles IR, zlepšuje integritu signálu a uvolňuje cenné nemovitosti na přední straně pro logické tranzistory. Přední slévárny zahájily sériovou výrobu pomocí této techniky, což představuje klíčový moment ve vývoji Moorova zákona. Návrháři nyní musí při výběru výrobního partnera zohlednit nová pravidla návrhu.

Pokročilé balení a integrace čipů

Definice „fab“ se rozšířila za hranice front-end výroby. V roce 2026, parádní stůl stále více zahrnuje funkce backend-of-line (BEOL), konkrétně pokročilé balicí služby, jako je 2.5D a 3D integrace. Éra monolitických čipů ustupuje modulárním konstrukcím.

Chiplety umožňují výrobcům kombinovat procesní uzly. Vysokorychlostní výpočetní matrice může být vyrobena na 3nm uzlu, zatímco I/O a paměťové komponenty používají vyspělé, nákladově efektivní uzly. Tato strategie optimalizuje výnos a snižuje celkové náklady na systém. Slévárny nabízející bezproblémovou integraci mezi front-end logikou a back-end balením zaznamenávají nejvyšší poptávku.

Porovnání skvělých tabulek 2026: Nejlepší modely a slévárny

Abychom se zorientovali v komplexním dodavatelském prostředí, sestavili jsme srovnávací analýzu předních výrobních modelů dostupných v roce 2026. parádní stůl srovnání zdůrazňuje klíčové rozdíly v pojmenovávání uzlů, technologiích balení a cílových aplikacích.

| Slévárenský model | Vedoucí uzel (2026) | Klíčová architektura | Packaging Tech | Primární zaměření |

| Řada TSMC N2 | 2nm (N2P) | GAA Nanosheet | CoWoS-L / SoIC | AI akcelerátory, mobilní |

| Samsung SF2 | 2nm (SF2LPP) | GAA MBCFET | I-CubeX | HPC, Automobilový průmysl |

| Intel 18A | 18 Angstrom | RibbonFET + BSPDN | Foveros Direct | Datové centrum, CPU klienta |

| GlobalFoundries | 12LP+ / RF | FinFET (zralé) | 2.5D interposery | IoT, Automobilový průmysl, 5G |

| UMC | 22nm / 28nm | Planární / FinFET | Standardní Bump | Ovladače displeje, PMIC |

Toto parádní stůl snímek odhaluje jasnou divergenci ve strategii. Zatímco TSMC a Samsung bojují o okraj logické hustoty, Intel využívá svou jedinečnou technologii zadního napájení, aby přeskočil konkurenty v energetické účinnosti. Mezitím speciální slévárny jako GlobalFoundries a UMC dominují sektoru vyspělých uzlů, který zůstává zásadní pro analogové, RF a integrované obvody pro správu napájení (PMIC).

Dynamika cen a struktury nákladů v roce 2026

Pochopení dopadů na náklady parádní stůl je zásadní pro rozpočtování a životaschopnost produktu. V roce 2026 se ceny waferů po volatilitě na začátku dekády stabilizovaly, ale pro špičkové uzly existuje zřetelná prémie. Cena za plátek již není jen o krocích litografie; zahrnuje nákladnou metrologii, kontrolu defektů a pokročilou režii na balení.

Špičková vs. ekonomika vyspělých uzlů

Cenová propast mezi uzly třídy 3nm a vyspělými 28nm procesy se prohloubila. 300mm wafer na 2nm uzlu může stát výrazně více než jeho předchůdci kvůli extrémní složitosti litografických vrstev EUV. Nicméně, náklady na tranzistor stále klesá, díky čemuž jsou pokročilé uzly životaschopné pro širší škálu aplikací než jen pro vlajkové smartphony.

- Cena masky: Sady fotomasek pro uzly pod 3nm zůstávají masivní počáteční investicí, často přesahující desítky milionů dolarů.

- Výnosové učení: První uživatelé platí „rizikovou prémii“. Jak výnosy dozrávají v průběhu roku 2026, efektivní náklady na dobrou matrici podstatně klesají.

- Doplňky k balení: Pokročilé balení může přidat 20–30 % k celkovým výrobním nákladům, ale je často nezbytné k dosažení výkonnostních cílů na úrovni systému.

Pro společnosti analyzující parádní stůl pro optimalizaci nákladů strategie často zahrnuje správnou velikost uzlu. Použití 5nm uzlu pro součást, která vyžaduje pouze 7nm výkon, vede ke zbytečným výdajům. Naopak nedostatečná specifikace může vést k tepelnému škrcení a špatné uživatelské zkušenosti.

Regionální cenové variace

Geopolitické faktory zavedly regionální cenové úrovně. Dotace ze zákona CHIPS v USA a podobné iniciativy v Evropě a Asii změnily efektivní strukturu nákladů pro místní produkci. Zatímco základní ceny waferů zůstávají celosvětově konkurenceschopné, celkové pořizovací náklady nyní zahrnují prémie za logistické zabezpečení a strategie ukládání zásob.

Manažeři dodavatelského řetězce musí hledět za hlavní cenu v parádní stůl. Musí zvážit dlouhodobé smlouvy o dodávkách (LTSA), poplatky za rezervaci kapacity a potenciál vládních pobídek, které mohou kompenzovat počáteční kapitálové výdaje. Flexibilita při získávání zdrojů v různých geografických regionech se stává standardním požadavkem na odolnost.

Strategické aplikace: Kdo potřebuje jaký model Fab?

Výběr správné položky z parádní stůl zcela závisí na doméně aplikace. V roce 2026 neexistuje žádné univerzální řešení. Různá průmyslová odvětví upřednostňují různé atributy, od hrubé rychlosti po dlouhodobou dostupnost a teplotní toleranci.

Umělá inteligence a vysoce výkonné počítače

U cvičných clusterů AI a inferenčních motorů je priorita maximální hustota tranzistoru a šířka pásma paměti. Tyto aplikace vyžadují nejnovější uzly (2nm/18A) spojené s pokročilým 2,5D nebo 3D balením. O schopnosti integrovat HBM (High Bandwidth Memory) přímo sousedící s logickou matricí nelze vyjednávat.

Společnosti v tomto odvětví pečlivě sledují parádní stůl pro přidělení kapacity CoWoS a Foveros. Nedostatky v balicích slotech často brzdí výrobu více než samotnou výrobu plátků. Zajištění kapacity zde vyžaduje víceleté závazky a úzkou spolupráci s týmy slévárenských inženýrů.

Automobilový a průmyslový IoT

Automobilový průmysl představuje jiný soubor požadavků. Spolehlivost, dlouhá životnost a provoz v drsném prostředí mají přednost před špičkovou rychlostí. V důsledku toho, parádní stůl položky pro 40nm, 28nm a 22nm FD-SOI uzly jsou pro tento segment vysoce relevantní.

- Bezpečnostní certifikace: Procesy musí podporovat normy ISO 26262 ASIL-D.

- Rozsah teplot: Čipy musí spolehlivě fungovat od -40°C do 150°C.

- Životnost dodávky: Životní cykly automobilů trvají 10–15 let a vyžadují zaručenou dostupnost procesu.

Zde excelují speciální slévárny, které nabízejí robustní možnosti analogového smíšeného signálu zabudované do vyspělých digitálních toků. Důraz je kladen spíše na minimalizaci výpadků v poli než na maximalizaci rychlosti hodin.

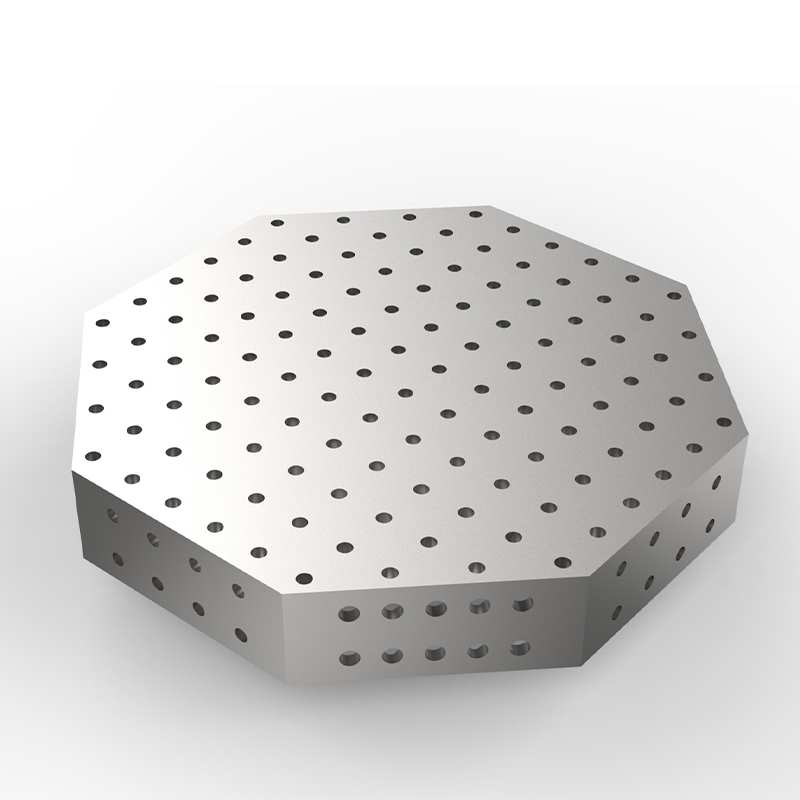

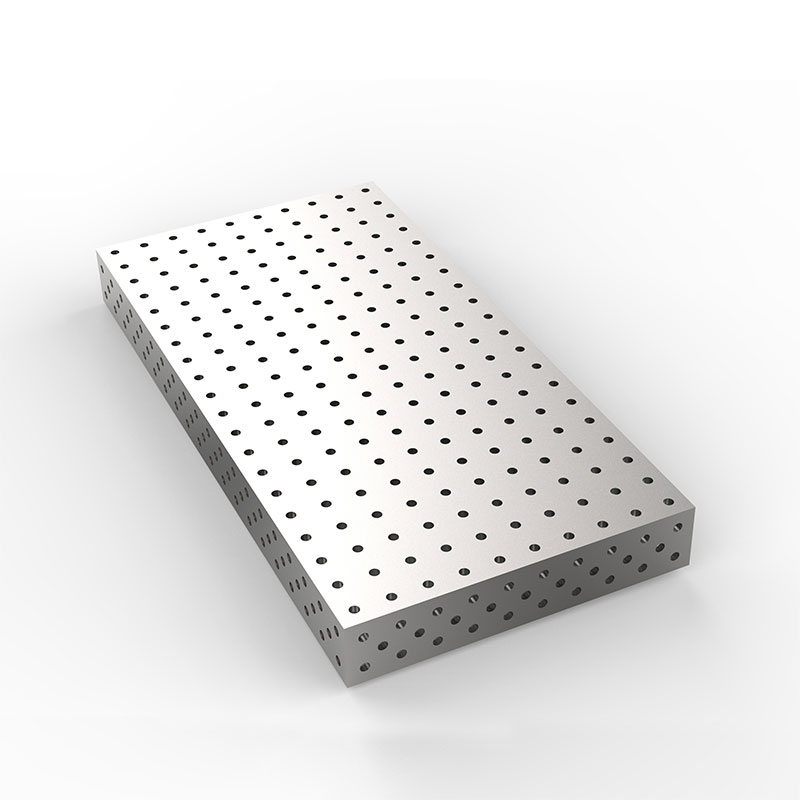

Přesnost požadovaná při výrobě polovodičů však přesahuje rámec křemíkového plátku až po fyzickou infrastrukturu podporující výrobu. Stejně jako návrháři čipů spoléhají na přesné tabulky, inženýři zařízení spoléhají na vysoce přesné nástroje, aby udrželi vyrovnání a stabilitu během montáže a testování. Botou Haijun Metal Products Co., Ltd. se v tomto ekosystému ukázala jako klíčový partner specializující se na výzkum, vývoj a výrobu vysoce přesných flexibilních modulárních přípravků a nástrojů pro obrábění kovů. Hlavní produktová řada společnosti Haijun Metal, která se zavázala poskytovat efektivní svářecí a polohovací řešení pro moderní výrobu, zahrnuje všestranné 2D a 3D flexibilní svařovací platformy. Tyto platformy, proslulé svou výjimečnou přesností, se staly preferovaným souřadnicovým zařízením v obráběcím, automobilovém a leteckém průmyslu – v odvětvích, která silně závisí na dodavatelském řetězci polovodičů. Jejich komplexní řada doplňkových komponent, jako jsou víceúčelové čtvercové boxy ve tvaru U a L, opěrné úhlové žehličky řady 200 a univerzální úhlové úhloměry 0-225°, se hladce integrují a umožňují rychlé polohování obrobku. Navíc jejich profesionální litinové 3D svařovací platformy a úhlové spojovací bloky zajišťují odolnost a stabilitu nezbytnou pro přísné požadavky výroby elektroniky. Díky dlouholetým zkušenostem v oboru slouží Haijun Metal jako důvěryhodný dodavatel na domácím i mezinárodním trhu a zajišťuje, že fyzické základy high-tech výroby jsou stejně robustní jako samotné čipy.

Spotřební elektronika a mobilní zařízení

Mobilní SoC jsou na průsečíku výkonu a energetické účinnosti. Životnost baterie je konečným omezením. Proto výrobci mobilních zařízení využívají parádní stůl najít sladké místo, kde zvýšení výkonu neohrozí tepelné obálky. Zde jsou rozhodující 3nm a 2nm uzly, které nabízejí nejlepší poměr výkonu na watt.

Navíc mobilní designy stále více využívají heterogenní integraci. Aplikační procesory, modemy a RF front-endy mohou být vyrobeny na různých uzlech a zabaleny dohromady. Tento přístup umožňuje návrhářům optimalizovat každý subsystém individuálně při zachování kompaktního tvaru.

Jak interpretovat a využívat data tabulky Fab

Přístup k a parádní stůl je pouze prvním krokem; správná interpretace dat vyžaduje odborné znalosti. Špatné čtení údajů o kapacitě nebo úrovních připravenosti technologie může vést ke katastrofálním zpožděním produktů. Zde je strukturovaný přístup k efektivnímu využití těchto dat.

Průvodce analýzou krok za krokem

- Definujte požadavky: Než se podíváte na jakákoli data, jasně načrtněte své cíle v oblasti výkonu, výkonu, oblasti a nákladů (PPAC).

- Filtrovat podle uzlu: Zúžit parádní stůl na uzly, které splňují vaše specifikace minimální hustoty a úniku.

- Vyhodnotit ekosystém: Zkontrolujte dostupnost IP, vyspělost návrhové sady a referenční toky pro vybraný uzel.

- Posoudit kapacitu: Podívejte se za nominální kapacitu. Prozkoumejte aktuálně dostupné sloty pro nové výstupy kazet ve vašem cílovém časovém rámci.

- Zkontrolujte zarovnání plánu: Zajistěte, aby byla budoucí cesta migrace slévárny v souladu s plány životního cyklu vašeho produktu.

Tento systematický přístup zajišťuje, že rozhodnutí jsou řízena daty, nikoli marketingovým humbukem. Pomáhá identifikovat potenciální úzká místa již ve fázi návrhu, čímž šetří čas a zdroje.

Běžná úskalí, kterým je třeba se vyhnout

Jednou z běžných chyb je předpoklad, že názvy uzlů jsou ve slévárnách ekvivalentní. „3nm“ uzel od jednoho dodavatele může mít jiné hustoty tranzistorů nebo rozteče hradel než jiný. Při kontrole vždy porovnávejte fyzické metriky spíše než marketingové štítky parádní stůl.

Dalším úskalím je ignorování backendových omezení. Fantastický front-end proces je k ničemu, pokud je související balicí technologie plně obsazena nebo je technicky nekompatibilní s vaší velikostí matrice. Holistické hodnocení je klíčem k úspěšnému vyřazení z pásek v komplexním prostředí roku 2026.

Často kladené otázky o tabulce Fab 2026

Jaká je nejkritičtější metrika ve skvělé tabulce pro AI startupy?

Pro startupy s umělou inteligencí je často nejdůležitější metrika dostupnost balení v kombinaci s výkon na watt. Zatímco hustota surového tranzistoru je důležitá, schopnost zabezpečit CoWoS nebo ekvivalentní pokročilé obalové sloty určuje, zda lze čip skutečně vyrobit a odeslat. Rozhodujícím faktorem je také přístup k paměťovým rozhraním s velkou šířkou pásma.

Jsou zralé uzly stále relevantní v roce 2026?

Absolutně. Vyspělé uzly (28nm a vyšší) nadále řídí většinu objemu polovodičových jednotek. Jsou nezbytné pro automobilový průmysl, průmysl, IoT a aplikace pro správu napájení. The parádní stůl ukazuje, že rozšiřování kapacity ve vyspělých uzlech pokračuje, aby uspokojilo trvalou poptávku, což dokazuje, že zůstávají základním kamenem odvětví.

Jak geopolitické napětí ovlivňuje data fab table?

Geopolitické napětí vedlo k fragmentaci parádní stůl. Data nyní často rozlišují mezi dostupnou kapacitou v různých regionech kvůli kontrole exportu a požadavkům na místní obsah. Plánovači dodavatelského řetězce musí ověřit geografický původ kapacity, aby zajistili soulad s mezinárodními obchodními předpisy.

Mohou malé společnosti přistupovat k špičkovým uzlům uvedeným v tabulce fab?

Přístup je možný, ale náročný. Špičkové uzly vyžadují značné investice NRE (Non-Recurring Engineering). Víceprojektové wafery (MPW) a cloudové přístupové programy nabízené velkými slévárnami však bariéry snižují. Malé společnosti mohou prototypovat na pokročilých uzlech, i když objemová výroba obvykle vyžaduje značné finanční prostředky a strategická partnerství.

Závěr a strategická doporučení

The parádní stůl pro rok 2026 je více než jen seznam specifikací; je to dynamická mapa globálního technologického prostředí. Odráží rok, kdy architektonické inovace, od GAA až po backside power, nově definují to, co je možné v křemíku. Pro podniky pohybující se tímto terénem je schopnost přesně interpretovat tyto datové body konkurenční výhodou.

Úspěch v tomto prostředí vyžaduje vyvážený přístup. I když je přitažlivost nejmenšího uzlu silná, optimální volbou je vždy ta, která nejlépe vyhovuje specifickým požadavkům na produkt, rozpočtovým omezením a časové ose. Ať už vytváříte další generaci akcelerátorů AI nebo spolehlivé automobilové ovladače, ten správný vstup do světa parádní stůl existuje pro vaše potřeby.

Kdo by měl tuto příručku používat? Produktoví manažeři, stratégové dodavatelského řetězce a hardwaroví architekti, kteří chtějí sladit své plány s realitou výroby. Pokud v nadcházejícím roce plánujete stažení pásky, začněte tím, že porovnáte své požadavky PPAC s nejnovějšími parádní stůl dat. Zapojte se včas se zástupci slévárny, abyste zajistili kapacitu a ověřili svou návrhářskou strategii. Budoucnost křemíku je jasná, ale dává přednost těm, kteří plánují s přesností a předvídavostí.